For many years, the compute trade has relied on Moore’s Legislation – and efficiently so. The precept that the variety of transistors on a chip doubles each two years has been the bastion of the digital age.

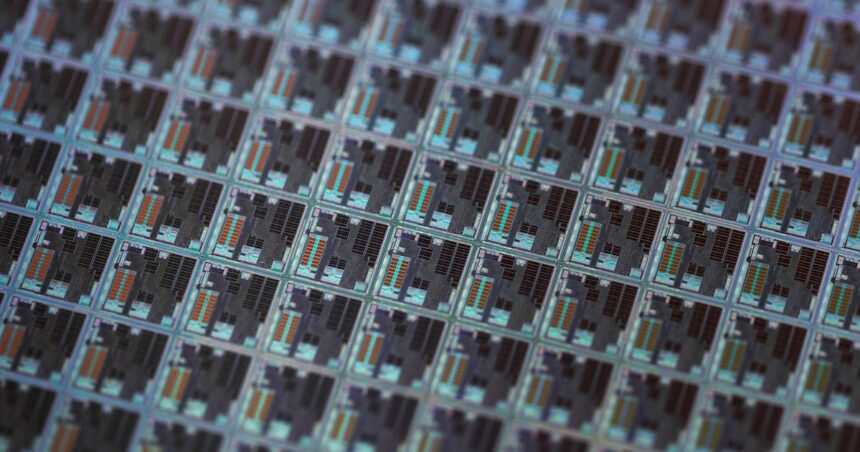

Nonetheless, the period of Moore’s Legislation is ending, simply as compute demand has by no means been extra meteoric. Transistor scaling is reaching its bodily restrict on the nanoscale, whereas the arrival of Gen AI is driving the necessity for multibillion-parameter AI fashions and coaching clusters requiring a whole bunch of 1000’s and even tens of millions of chips for a single mannequin.

The underlying battleground of compute is altering – as an alternative of innovating new methods to drive efficiency from a single chip, there should be a elementary rethinking on the scale of a whole bunch, 1000’s, and even tens of millions of chips on a per-system and per-rack foundation.

Amdahl’s Legislation for AI Scale Success

For rack-scale considering, Amdahl’s Legislation tells us that even probably the most superior GPUs can’t ship their theoretical efficiency with out addressing the challenges distinctive to the system degree. Interconnects should shuffle information between chips at blistering speeds, cooling programs should extract tens of kilowatts of warmth per rack, and energy supply architectures should reliably feed 1000’s of processors operating at near-constant peak load.

We are able to draw on some classes from our previous. In the course of the mainframe and minicomputer eras, processor enhancements alone have been initially ample to ship efficiency positive factors. Nonetheless, as workloads ballooned in complexity, differentiation got here from the shift to systems-level orchestration.

The reply was client-server architectures and virtualization, which finally led to what we now know as cloud computing. Within the AI period, this sample is repeating: true effectivity and efficiency enhancements will emerge solely when every part of a rack system is co-optimized. This represents greater than a technical nuance – it represents a radical inflection level in how computing infrastructure is constructed, scaled, and monetized.

Main trade incumbents have already acknowledged this shift. Nvidia has acquired Mellanox, Cumulus Networks, and Augtera, with Enfabrica rumored to be subsequent. The corporate is constructing a formidable networking stack to enhance its GPUs and ship holistic rack-level options. Extra not too long ago, AMD acquired ZT Methods, a rack-level infrastructure and information heart programs supplier, to internalize programs design experience vital for AI.

The place Startups Match In

Regardless of heavyweight gamers working to consolidate and vertically combine on the rack scale, a number of distinctive gaps stay that hyperscalers and chip incumbents can’t – or doubtless is not going to – handle alone. These gaps are ripe for startup disruption.

Interconnects are the spine of system- and rack-level communication, the place even minor bottlenecks between compute nodes can cripple efficiency and improve latency.

Assembly the unprecedented bandwidth calls for of all-to-all communication throughout 1000’s of GPUs requires novel interconnect options that stability price, velocity, and vitality effectivity.

A vital dimension of this evolution is photonics, each on-chip and off-chip. Co-packaged optics and built-in photonics are reshaping swap and compute node integration by inserting optical interfaces instantly beside or inside chips, chopping energy consumption whereas boosting bandwidth density.

In the meantime, multipoint-to-multipoint photonic networks are rising as a path to really scalable all-to-all GPU communication, enabling bigger clusters and unprecedented effectivity for AI workloads.

Startups are driving a lot of this innovation, as evidenced by latest acquisitions equivalent to Ciena’s acquisition of Nubis Communications, a TDK Ventures portfolio firm, and Credo’s buy of Hyperlume.

Along with advances in connectivity and bandwidth, {hardware} and software program should be tightly paired and intelligently orchestrated to unlock true efficiency. Rack-aware AI options, as an example, present large promise by adapting software program to {hardware} topology, structure, and bandwidth as an alternative of forcing {hardware} to evolve to software program constraints.

Meta has already embraced this strategy, designing “AI Zones” inside their racks that leverage specialised rack coaching switches (RTSWs) and customized algorithms to optimize GPU communication for large-scale language mannequin coaching.

Lastly, there’s a monumental alternative in energy administration, distribution, and cooling because the trade should rise to fulfill the challenges of responsibly dealing with and mitigating the tens of kilowatts per rack which can be generated in in the present day’s information facilities.

An Investor’s Perspective

For traders, the sign is obvious: the subsequent wave of AI infrastructure winners is not going to be outlined solely by who makes the quickest chip, however by who allows rack-scale efficiency. Historical past affords precedent.

Simply as Cisco and Arista rose to prominence by fixing campus and information heart networking, and VMware outlined an period by virtualization and orchestration, the approaching decade will crown system-level innovators as indispensable to AI’s infrastructure spine.

The AI “chip wars” are evolving into “system wars.” In that transition, the best alternatives and returns will accrue to those that can engineer at scale.