We wish to hear from you! Take our fast AI survey and share your insights on the present state of AI, the way you’re implementing it, and what you anticipate to see sooner or later. Learn More

Applied Materials has revealed chip wiring improvements that may assist tackle challenges in the way in which of energy-efficient computing.

The usage of new supplies in chip wiring will allow two-nanometer node manufacturing, the place the width between circuits is round two billionths of a meter aside. These improvements will scale back resistance in wiring as a lot as 25% and new supplies will scale back chip capacitance by as much as 3%.

Chip makers are utilizing the advances within the manufacturing of logic chips now and reminiscence chip makers (who make dynamic random entry reminiscence, or DRAM) are evaluating it now for improved 3D chip stacking.

The mission is to in the end allow gear that may construct a trillion-transistor chip similar to a graphics processing unit, in keeping with a narrative within the IEEE Spectrum journal. It’s robust to maintain up with the tempo of Moore’s Regulation, the 1965 prediction by former Intel CEO Gordon Moore that holds the variety of parts on a chip will double each couple of years. As a substitute of getting smaller, chips are getting larger and a number of chips are being built-in right into a single resolution utilizing superior packaging.

Countdown to VB Remodel 2024

Be part of enterprise leaders in San Francisco from July 9 to 11 for our flagship AI occasion. Join with friends, discover the alternatives and challenges of Generative AI, and discover ways to combine AI purposes into your {industry}. Register Now

The nice factor is that the chip {industry} has been in a position to get a 3 times enchancment each two years over the previous 15 years. To do that, it must hold growing new supplies, stated Alex Jansen, director of product advertising at Utilized Supplies, in an interview with VentureBeat.

“To proceed this, we want new supplies,” Jansen stated. “There are a number of methods: patterning, transistors, wiring and superior packaging. We’re specializing in wiring.”

And wiring is necessary. Latest chips have greater than 60 miles of copper interconnect, 18 steel layers and 4 or 5 important layers, he stated. Each chip is a big 3D community of wires, Jansen stated.

Utilized Supplies is the most important maker of semiconductor manufacturing gear, and it revealed the advances on the Semicon West occasion in San Francisco as we speak. The corporate stated the supplies engineering improvements are designed to extend the performance-per-watt of pc programs by enabling copper wiring to scale to the 2nm logic node and past.

“The AI period wants extra energy-efficient computing, and chip wiring and stacking are important to efficiency and energy consumption,” stated Prabu Raja, president of the Semiconductor Merchandise Group at Utilized Supplies, in an announcement. “Utilized’s latest built-in supplies resolution permits the {industry} to scale low-resistance copper wiring to the rising angstrom nodes, whereas our newest low-k dielectric materials concurrently reduces capacitance and strengthens chips to take 3D stacking to new heights.”

Overcoming the physics challenges of basic Moore’s Regulation scaling

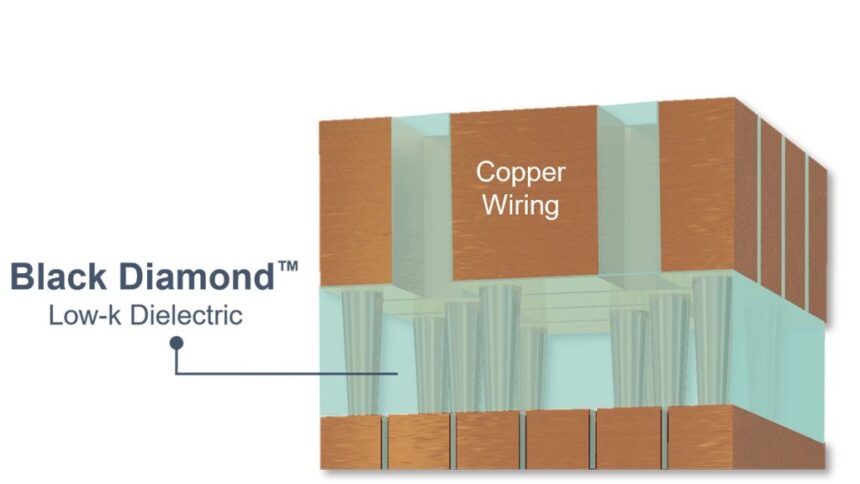

At this time’s most superior logic chips can include tens of billions of transistors linked by greater than 60 miles of microscopic copper wiring. Every layer of a chip’s wiring begins with a skinny movie of dielectric materials, which is etched to create channels which can be stuffed with copper.

Low-k dielectrics and copper have been the {industry}’s workhorse wiring mixture for many years, permitting chipmakers to ship enhancements in scaling, efficiency and power-efficiency with every technology.

Nevertheless, because the {industry} scales to 2nm and under, thinner dielectric materials renders chips mechanically weaker, and narrowing the copper wires creates steep will increase in electrical resistance that may scale back chip efficiency and improve energy consumption.

Enhanced Low-k dielectric reduces interconnect resistance and strengthens chips for 3D stacking

Utilized stated its Black Diamond materials has led the {industry} for many years, surrounding copper wires with a low-dielectric-constant – or “k-value” – movie engineered to scale back the buildup {of electrical} expenses that improve energy consumption and trigger interference between electrical alerts.

Utilized as we speak launched an enhanced model of Black Diamond, the newest within the firm’s Producer Black Diamond PECVD (plasma-enhanced chemical vapor deposition) household. This new materials reduces the minimal k-value to allow scaling to 2nm and under, whereas providing elevated mechanical energy which is turning into important as chipmakers and programs firms take 3D logic and reminiscence stacking to new heights.

Ajay Bhatnagar, managing director of product advertising, stated in an interview with VentureBeat that the dielectric deposition group has been engaged on the capacitance aspect of the issue.

“We’re very enthusiastic about introducing latest improvements in what we name Enhanced Black Diamond,” he stated.

It’s a brand new chemical vapor deposition materials used for shoring up trenches and insulating the wires from binary supplies.

“You’ll be able to consider this as a matrix into which this mesh of copper wiring is embedded into,” Bhatnagar stated. “We’re surrounding the wires with very low-k dielectric fixed. And the movie is admittedly engineered to scale back the buildup {of electrical} expenses that may improve energy consumption and trigger interference between {the electrical} alerts.”

“At this time, we’re introducing a brand new class of those Black Diamonds that we name enhanced. The principle profit is that this new materials reduces the important thing worth of the dielectric fixed, which permits prospects to scale to 2 nanometers and under,” Bhatnagar stated. “However on the identical time, it will increase the mechanical energy, which is now turning into actually actually important. As chip makers and system firms take 3D logic and reminiscence stacking to new heights, mechanical energy and a price grow to be very important.”

He stated the improved Black Diamond know-how is being now adopted by all main logic and reminiscence chip makers.

“One of many greatest challenges for us within the low-k materials aspect for this matrix must be to interrupt the commerce off between dielectric fixed and mechanical energy,” Bhatnagar stated. “Prospects wish to push decrease and decrease dielectric fixed as a result of that helps when it comes to decreasing the capacitance and the sign noise between the traces.”

“There’s a commerce off between getting the dielectric fixed down, in addition to growing the mechanical energy of the dielectric. This new materials that we’ve engineered on the molecular stage has damaged this commerce off that existed. What we’ve carried out with molecular engineering when it comes to this matrix is created a brand new low-k materials, which has damaged that commerce off.”

“We’re making an attempt to decrease the capacitance, and a method to try this is to decrease what we name the dielectric fixed. Capacitance is straight proportional to this fixed. We’re reducing that and on the identical time we’re growing the mechanical energy,” stated Bhatnagar. “Usually, there’s a tradeoff with that. So with this new molecule that we put into the improved Black Diamond, we’ve got been in a position to break this tradeoff and transfer the curve.”

To scale chip wiring, chipmakers etch every layer of low-k movie to create trenches, then deposit a barrier layer that forestalls copper from migrating into the chip and creating yield points. The barrier is then coated with a liner that ensures adhesion in the course of the ultimate copper reflow deposition sequence, which slowly fills the remaining quantity with copper.

As chipmakers additional scale the wiring, the barrier and liner take up a bigger share of the amount meant for wiring, and it turns into bodily not possible to create low-resistance, void-free copper wiring within the remaining area.

At this time, Utilized Supplies launched its newest IMSTM (Built-in Supplies Answer) which mixes six completely different applied sciences in a single high-vacuum system, together with an industry-first mixture of supplies that permits chipmakers to scale copper wiring to the 2nm node and past. The answer is a binary steel mixture of ruthenium and cobalt (RuCo), which concurrently reduces the thickness of the liner by 33 % to 2nm, produces higher floor properties for void-free copper reflow, and reduces electrical line resistance by as much as 25% to enhance chip efficiency and energy consumption.

The main target has been to make the wiring higher and enhance the dielectric on the wiring. Because the options shrink, it will get tougher to place copper wiring into the trenches with out creating what are generally known as voids, the place there’s a part that didn’t get copper into it. This impacts resistance and yield as nicely. Resistance retains coming again as an issue with every technology of chips.

Now the corporate is switching to a mixture of ruthenium and cobalt because the liner between the copper and the movie. It may scale back the thickness of the liner by as much as 33%. The result’s there may be extra room for the copper within the trench, and that widens the efficient wire, which lowers the resistance. Efficiency goes up. The width of those sections within the construction is microscopic and it leads to higher yields.

The brand new Utilized Endura Copper Barrier Seed IMS with Volta Ruthenium CVD (chemical vapor deposition) is being adopted by all main logic chipmakers and started transport on the 3nm node. An animation might be viewed here.

“Whereas advances in patterning are driving continued machine scaling, important challenges stay in different areas together with interconnect wiring resistance, capacitance and reliability,” stated Sunjung Kim, VP and head of the foundry growth Crew at Samsung Electronics, in an announcement. “To assist overcome these challenges, Samsung is adopting a number of supplies engineering improvements that reach the advantages of scaling to essentially the most superior nodes.”

“The semiconductor {industry} should ship dramatic enhancements in energy-efficient efficiency to allow sustainable development in AI computing,” stated Y.J. Mii, EVP and co-COO at TSMC, in an announcement. “New supplies that scale back interconnect resistance will play an necessary function within the semiconductor {industry}, alongside different improvements to enhance general system efficiency and energy.”

A rising wiring alternative

Utilized is the {industry} chief in chip wiring course of applied sciences. From the 7nm node to the 3nm node,

interconnect wiring steps have roughly tripled, growing Utilized’s served out there market alternative by greater than $1 billion per 100,000 wafer begins monthly (100K WSPM) of greenfield capability, to roughly $6 billion.

Wanting forward, the introduction of bottom energy supply is predicted to extend Utilized’s wiring alternative by one other $1 billion per 100K WSPM, to roughly $7 billion.

One analysis initiative that Intel just lately talked about centered on making wiring higher via the bottom of a chip, which usually isn’t used for wiring. This architectural change takes energy traces from the entrance of the chip to the bottom, the place the wiring must be thicker. However frontside wiring wants enhancements as nicely, and so these enhancements are all occurring in parallel, Jansen stated.

The addition of bottom wiring reduces complexity and that helps get extra environment friendly routing and higher efficiency and energy consumption, Jansen stated. However the frontside enhancements are additionally essential to allow scaling.

About 20 years in the past, the wiring moved away from aluminum to dielectrics and copper. To drive extra efficiency yearly, the {industry} has been including extra supplies to create stronger wires which can be extra vitality effectivity. The chip gear etches trenches and vias into the movie on the chip surfaces, after which in the end fills these gaps with copper for wiring. Copper is the principle technique to conduct electrons via the chip. Now the supplies function a barrier between the copper and the dielectric in order that they don’t contaminate one another.

“With out supplies innovation, the limitations and the liners are beginning to occupy increasingly more of that trench quantity. So this scaling creates a few completely different challenges. As copper wires shrink, resistance goes up. That is form of a fundamental physics (reality). Thinner wires are going to create greater resistance. There isn’t actually a great way round that,” Jansen stated.

He added, “And so what we’re making an attempt to do is enhance the quantity of that wire that’s devoted to transform. Secondly, as these items shrink, the wires are getting nearer and nearer collectively. And so there’s much less area for the dielectric that’s surrounding them. And because of this, you might have electrical crosstalk. You will get sign delays, distortion, and altogether this value in efficiency and energy consumption. In order that’s the alternative of what we’re making an attempt to do.”

To make enhancements for demanding AI chips, the efficiency and effectivity has to maintain getting higher.

The brand new chip wiring merchandise, together with different supplies engineering improvements for making future AI chips, will probably be mentioned at Applied’s Semicon West 2024 Technology Breakfast.

Higher GPUs and AI chips

All of this work is geared toward making higher GPUs and different AI chips that may deal with the calls for of the longer term, the Utilized Supplies spokesmen stated. They see these wiring developments as serving to the chip {industry} keep on the trail of 3 times enchancment each two years for vitality effectivity.

“That is an enabling know-how for 2nm and past,” Jansen stated.

Bhatnagar added that stacking reminiscence chips is critical for feeding knowledge to AI processors, and excessive mechanical energy is required for the 3D stacking capacity. The tech right here permits the chips to succeed in excessive computing efficiency with out melting down.

“That is among the causes we’re driving these supplies — due to the AI necessities for high-bandwidth reminiscence,” Bhatnagar stated.

Consequently, Jansen stated, “I believe the cadence at which new applied sciences proceed to increase Moore’s Regulation and the densification of the transistors per space is aligned with that” analysis within the estimates round reaching a trillion-transistor GPU. Nvidia’s Blackwell has about 208 billion transistors on it. AMD will probably be becoming a member of Utilized Supplies at its occasion his week.

Source link